6 Layer Prototype Service

Pricing

$15 per square inch, which includes three copies of your design.

For example, a 2 square inch board would cost $30 and you’d get three copies of your board. You can order as many copies as you want, as long as they’re in multiples of three.

Turn Times

Orders will ship within 9-14 calendar days of ordering.

You can get a quote, approve a design, and pay for an order at OSH Park.

We do not offer Super Swift Service for six layer boards.

We do not offer Medium Run Services on 6 layer boards, but we may be able to discount orders over 100 square inches. Contact [email protected] with your design for more information.

Common Specs

These specs apply to all our PCB services.

| Spec | Value | |

|---|---|---|

| Manufactured in the United States | Yes | |

| Lead Free compatible | Yes | |

| RoHS Compliant | Yes | |

| High Temp | Yes, 175 Tg or higher (see Material Specs) | |

| PCB Finish | ENIG (Gold), compliant with IPC-4552 | |

| Soldermask Type | SMOBC (Soldermask Over Bare Copper), both sides | |

| Silkscreen Type | High Res DLP, both sides |

Stackup

| Thickness | Layer | Tolerance | dk | df |

|---|---|---|---|---|

| 0.6 mil (0.0152mm) | silkscreen | +/-10% (0.2mil,0.00508mm) | ||

| 0.6 mil (0.0152mm) | solder resist | +/-10% (0.2mil,0.0051mm) | ||

| 1.7 mil (0.0432mm) | 1 oz copper clad+plated | |||

| 4.36 mil (0.1107mm) | FR408HR 106 75% prepreg | +/-10% (0.436mil,0.0111mm) | 3.23@1Ghz | 0.011 |

| 0.68 mil (0.0175mm) | 0.5 oz copper clad | |||

| 4 mil (0.1016mm) | FR408HR 2113 core | +/-10% (0.4mil ,0.0102mm) | 3.66@1Ghz | 0.009 |

| 0.68 mil (0.0175mm) | 0.5 oz copper clad | |||

| 36.44 mil (0.9256mm) | FR408HR core |

+/-10% (3.64mil,0.0925mm) | ||

| 0.68 mil (0.0175mm) | 0.5 oz copper clad | |||

| 4 mil (0.1016mm) | FR408HR 2113 core | +/-10% (0.4mil ,0.0102mm) | 3.66@1Ghz | 0.009 |

| 0.68 mil (0.0175mm) | 0.5 oz copper clad | |||

| 4.36 mil (0.1107mm) | FR408HR 106 75% prepreg | +/-10% (0.436mil,0.0111mm) | 3.23@1Ghz | 0.011 |

| 1.7 mil (0.0432mm) | 1 oz copper clad+plated | |||

| 0.6 mil (0.0152mm) | solder resist | +/-10% (0.2mil,0.0051mm) | ||

| 0.6 mil (0.0152mm) | silkscreen | +/-10% (0.2mil,0.00508mm) |

Material Specs

| Spec | Value | |

|---|---|---|

| Substrate | 175Tg FR4 | ISOLA FR408-HR Datasheet PDF |

| Board Thickness | 63mil (1.6mm) nominal | |

| Dielectric | See stackup | |

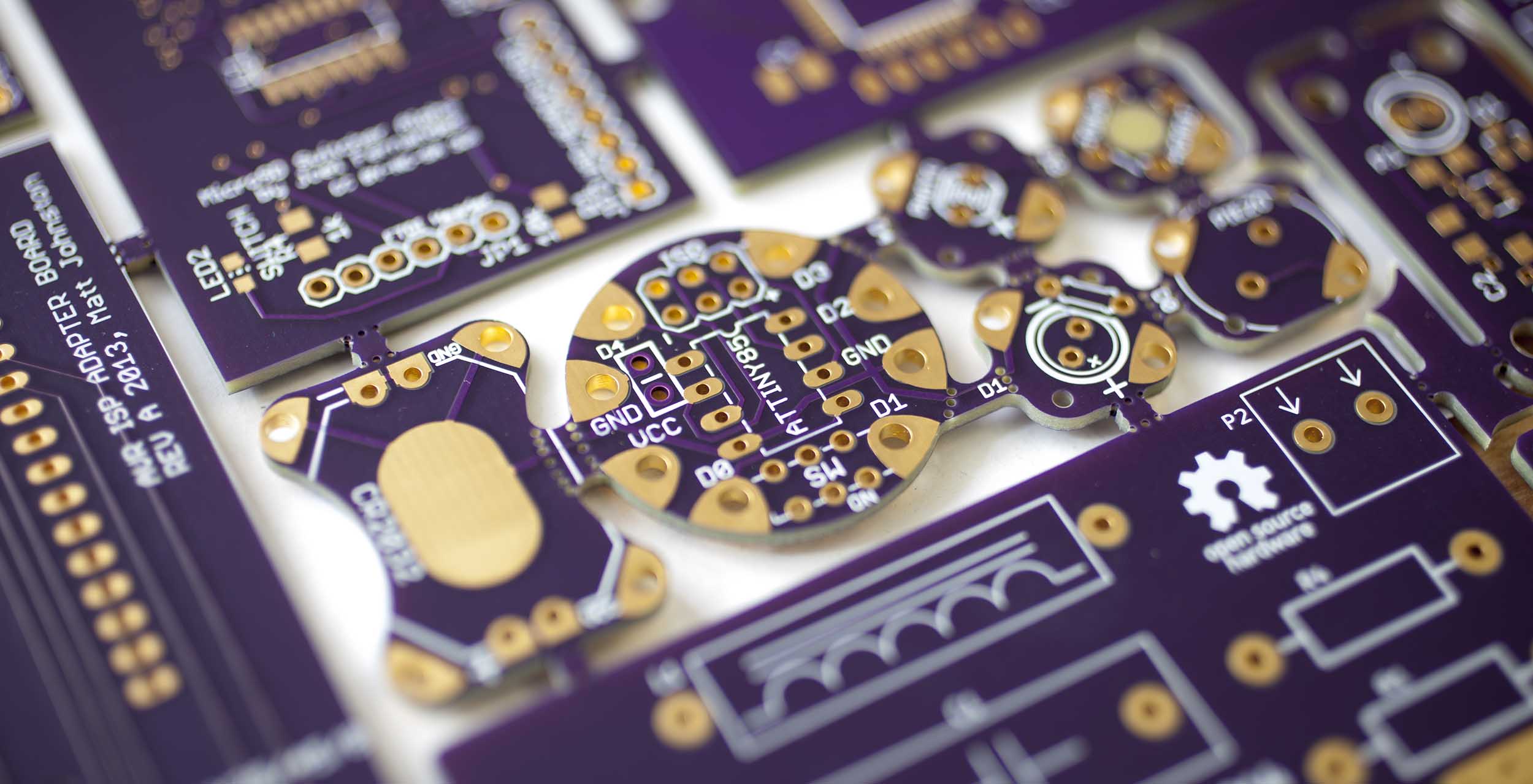

| Soldermask Color | Purple | Mask Datasheet |

| Minimum soldermask web | 4 mil (0.1016mm) | |

| Maximum soldermask alignment | 3mil (0.0762mm) | Covers retraction, expansion, and shift |

| Silkscreen minimum line width | 5 mil (0.127mm) (recommended minimum) 3 mil (0.0762mm) (short lines, text, graphics) |

Silkscreen Datasheet |

| Maximum board size | 16in (406.4mm) by 22in (558.8mm) | |

| Minimum board size | 0.25in (6.35mm) by 0.25in (6.35mm) |

Copper Specifications

| Spec | Value | |

|---|---|---|

| Copper Layers | 6 | |

| Copper Weight | 1oz outer 1/2oz inner |

|

| Trace Spacing | 5mil (0.127mm) | |

| Trace Width | 5mil (0.127mm) | |

| Annular Ring | 4mil (0.1016mm) | |

| Board Edge Keepout | 15mil (0.381) from nominal board edge | |

| Via Plating Thickness | 1mil (0.0254mm) | |

| Plated Drill to Internal Layer Copper Clearance | 10mil (0.254mm) |

Drill Specifications

| Spec | Value | |

|---|---|---|

| Minimum Annular Ring | 4mil (0.1016mm) | |

| Minumum Drill Size | 8mil (0.2032mm) | |

| Minimum Slot Size | 20mil (0.508mm) (drill slot only) | Additional information on slots |

| Drill Size tolerance | Max: +/- 2.5mil (0.0635mm) Typical: +/- 1.0mil (0.0254) |

|

| Drill Positional Tolerance | Max: 2mil (0.0508mm) Typical: <1mil (0.0254mm) |

|

| Via Tenting | Yes (filled hole and flat surface not guaranteed) | |

| Buried Via | No | |

| Blind Via | No | |

| Filled+Plated Vias (via-in-pad) | No | |

| Overlapping drills | Allowed, but not guaranteed. May result in missing or slotted holes. 5 mil (0.127mm) clearance is recommended between holes. |

|

| Castellations | Allowed, but not guaranteed | Details and recommendations |

| Maximum Drill Size | None | Drill sizes above 250mil (6.35mm) will be fabbed, but with larger milling tolerances. |

| Plated Drill to Internal Layer Copper Clearance | 10mil (0.254mm) |

Layer Naming

We automatically detect intended layer order from many tools, using common naming conventions and meta-data formats like Gerber X2. In most cases, renaming files should not be needed, and you can use your default export settings.

If your tool or files requires configuration or manual renaming of layers, we suggest this pattern to ensure your layer order is interpreted correctly.

| Layer | File Extension | Layer Placement order |

|---|---|---|

| Layer 1 | .GTL | Top or Front layer |

| Layer 2 | .G2L | Internal layer (adjacent to Top) |

| Layer 3 | .G3L | Internal layer (top side of core) |

| Layer 4 | .G4L | Internal layer (bottom side of core) |

| Layer 5 | .G5L | Internal layer (adjacent to Bottom) |

| Layer 6 | .GBL | Bottom or Back layer |

For additional info or other layers, see our Suggested Naming Pattern

Internal Plane Polarity

When submitting gerbers, we need the “positive” internal planes, meaning that lines represent copper, not the absence of copper.

Some CAD tools will generate the internal planes as power planes with “negative” polarity so the lines indicate where copper should be removed. To work around this, declare the internal planes as signal layers and use a copper pour to define the power plane.

Take a look at our [Positive and Negative Gerbers][invertedgerbers] page for more information.

Drill Internal Layer Clearance

Some tools will often suppress annular rings on vias that do not connect to internal layers. However, this may not accurately capture required production specs, leading to inadvertent spec violations. While these violations do not always result in issues, they can lead to surprising defects and yield issues.

This DRC requirement is not always obvious inside design tools, with some tools defaulting to a violation, and not providing clear warnings. Care should be taken to ensure compliance. Tools handle this differently, but one of the following methods should help:

- Configuring the tool to always include annular rings, regardless of net connections

- Increasing ground plane clearance on internal layer copper pours

- Configuring custom net rules to increase isolation on internal layer copper pours.

Your design tool’s documentation will assist with these steps.